Lam Research et IBM visent l’objectif d’une puce IA à moins de 1 nm grâce à la High-NA EUV Bet — Est-ce la solution à la barrière physique face à la baisse de rendement ?

Repousser les limites de la loi de Moore : la collaboration ambitieuse entre IBM et Lam Research

IBM et Lam Research se sont engagés dans une initiative majeure à long terme visant à redéfinir l’avenir de l’informatique en faisant progresser l’intégration logique en dessous du seuil de 1 nm. Ce partenariat de cinq ans est axé sur le développement de matériaux innovants, de techniques de fabrication de pointe et de la lithographie EUV à grande ouverture numérique (High-NA EUV) afin de propulser la feuille de route technologique d’IBM. Loin des améliorations incrémentielles, cet effort s’attaque directement aux barrières physiques fondamentales qui menacent de freiner la progression rapide des capacités de calcul.

Le rôle de la lithographie EUV à grande ouverture numérique

La lithographie High-NA EUV est au cœur de ce bond technologique. En tant que principal moteur de la miniaturisation accrue, elle permet de graver des motifs avec des pas aussi petits que 16 nm. Contrairement aux systèmes EUV actuels à faible ouverture numérique (Low-NA EUV), la High-NA EUV offre une amélioration de 67 % de l’ouverture numérique, ce qui se traduit par une résolution plus nette et potentiellement une simplification des processus de fabrication. Alors que des fondeurs de premier plan comme TSMC n’ont pas encore mis en œuvre cette technologie—privilégiant temporairement des stratégies multifragmentées complexes—IBM et Lam Research travaillent à accélérer l’adoption dans l’industrie grâce à la recherche sur les résines sèches High-NA EUV et à des innovations procédurales.

Une approche globale de l’intégration 3D

Réussir dans cette nouvelle ère de conception de puces exige plus que de simples avancées isolées. Comme le souligne le CTO de Lam, le véritable progrès dans l’intégration 3D repose sur une approche intégrée—associant matériaux, process et lithographie au sein d’un système unifié à haute densité. Les recherches de la communauté scientifique d’imec confirment que pour libérer tout le potentiel de la High-NA EUV, il est nécessaire d’optimiser conjointement matériaux, patterning, masques, imagerie, métrologie et conception. Traiter ces domaines de façon isolée ne suffit pas à surmonter les défis complexes à venir.

Investissement stratégique pour la prochaine génération de puces d’IA

Cette collaboration représente un investissement réfléchi dans la prochaine phase du progrès technologique. En combinant l’expertise en recherche d’IBM et les solutions de process complètes de Lam, le partenariat vise à développer et valider des chaînes de fabrication complètes pour les dispositifs de pointe à nanosheets et nanostacks. Leur objectif commun est d’établir un flux de fabrication fiable et performant pour les futures puces d’IA, garantissant que la puissance de calcul reste en phase avec les exigences de la révolution technologique à venir.

Dynamique du marché : opportunités de croissance et défi de l’adoption du High-NA EUV

Les perspectives commerciales de l’initiative sub-1nm d’IBM et Lam sont façonnées par deux puissantes dynamiques de croissance. Le marché plus large des équipements de fabrication de semi-conducteurs connaît une expansion rapide, alimentée par la demande inlassable des secteurs de l’IA, de l’IoT et de la 5G. Les prévisions de l’industrie estiment que le marché de ces équipements croîtra à un taux annuel moyen de 14,8 % entre 2026 et 2033. Cette poussée crée un environnement favorable pour les entreprises capables de proposer des solutions de fabrication de nouvelle génération.

Cependant, au sein de cette croissance fulgurante, un écart significatif demeure. Le segment dédié aux systèmes de lithographie avancée—pièce centrale de l’alliance IBM-Lam—connaît une progression plus régulière mais conséquente de 7,5 % de CAGR, avec des projections atteignant 31,16 milliards de dollars d’ici 2030. Ce rythme plus modéré reflète le cycle d’investissement des nœuds avancés. Le véritable défi ne réside pas dans la taille du marché, mais dans l’accélération de l’adoption de la High-NA EUV, qui en est encore à ses débuts chez les leaders de l’industrie.

À ce jour, des fondeurs comme TSMC n’ont pas encore opéré la transition vers la High-NA EUV pour la production de masse, préférant s’en remettre à une multi-lithographie complexe et coûteuse à l’aide des outils Low-NA EUV existants. Cela crée un écart important entre les capacités actuelles et le potentiel futur qu’IBM et Lam entendent débloquer. Leur succès reposera non seulement sur des avancées techniques, mais aussi sur l’accélération de l’adoption industrielle de la High-NA EUV.

En fin de compte, l’avantage du partenariat dépendra de sa capacité à dépasser le rythme naturel d’adoption de l’industrie. En menant à bien le co-développement de matériaux, de process et de lithographie, IBM et Lam cherchent à raccourcir la route vers les nœuds sub-1nm et rendre la High-NA EUV plus accessible et abordable. Dans un marché où les investissements en équipements croissent rapidement, être les premiers à valider un flux de process performant pourrait offrir un avantage compétitif non négligeable. La croissance exponentielle du marché est certaine—le défi consiste à bâtir l’infrastructure capable de la soutenir.

Perspectives financières à long terme : investissement R&D et le « yield cliff »

Les retombées financières de cette collaboration s’évaluent non pas en retours immédiats, mais en positionnement stratégique sur le long terme. Il s’agit là d’un investissement classique à long terme en recherche et développement, sans calendrier précis de commercialisation ni partenaires fondeurs annoncés. L’absence de précisions à court terme met en lumière les risques techniques considérables et la longue courbe d’adoption à prévoir. Pour les parties prenantes, la vraie valeur réside dans les succès de conception futurs plutôt que dans les bénéfices à court terme.

Sur le plan stratégique, Lam Research intègre ses technologies Aether dry resist, Kiyo etch et ALTUS Halo deposition dans l’infrastructure de recherche NanoTech d’IBM à Albany, co-développant ainsi des chaînes de process pour les dispositifs futurs à nanosheets et nanostacks. Cette collaboration étroite vise à assurer la présence de Lam lors de la prochaine vague de miniaturisation logique, afin que ses outils soient pris en compte dès les premières décisions de conception par les grands fondeurs et fabricants de puces. Ce partenariat témoigne d’un engagement durable pour faire progresser l’intégration logique, en ligne avec la montée en puissance des technologies d’attaque plasma et de dépôt requises par l’IA.

Le risque le plus important reste cependant d’ordre physique plus que commercial. Le « mur physique » du sub-1nm constitue un défi de taille, les variations à l’échelle atomique dans les matériaux et les procédés devenant la principale source de défauts. Cela conduit au fameux « yield cliff », où la part de puces fonctionnelles s’effondre en raison d’imperfections incontrôlables. Comme le révèle la recherche d’imec, exploiter pleinement le potentiel de la High-NA EUV nécessite une approche globale et systémique—le moindre maillon faible peut compromettre l’ensemble du process et le rendement des produits.

Surmonter ce défi exigera un investissement continu, car franchir le « yield cliff » est indispensable pour rendre viables les chaînes de fabrication avancées. Le succès du partenariat dépendra de sa capacité à transformer les avancées conjointes dans la résine sèche High-NA EUV et les technologies de process en trajectoires de production éprouvées à haut rendement. Tant que cela ne sera pas réalisé, les gains financiers resteront en suspens, dépendant de la capacité de l’industrie à maîtriser les défis de la fabrication à l’échelle atomique.

Jalons clés et indicateurs : suivre les progrès vers le prochain paradigme informatique

L’avenir de ce partenariat continue de se dessiner, avec des étapes charnières encore à atteindre. Pour les investisseurs et observateurs du secteur, repérer des signes tangibles de progrès sera essentiel pour juger si ce pari fondamental prend de l’ampleur ou rencontre des obstacles insurmontables.

- Validation expérimentale : Le premier jalon majeur consiste à démontrer les capacités du High-NA EUV en laboratoire. L’ouverture du ASML-imec High NA EUV Lithography Lab offre une première occasion de tester le potentiel de cette technologie. Le succès se mesurera à la capacité du labo à atteindre les objectifs de miniaturisation et de simplification du process sur des tranches tests réelles, fournissant la preuve de concept essentielle à l’adoption par l’industrie.

- Expansion de l’écosystème : Le prochain indicateur clé sera l’implication de partenaires industriels supplémentaires. Si IBM et Lam n’ont pas encore annoncé de collaborateurs pour la fabrication de puces, une participation large est vitale pour la commercialisation. L’annonce de l’entrée de grandes fonderies ou fabricants logiques dans l’initiative sub-1nm—potentiellement via des partenariats similaires avec ASML et imec—signe une confiance accrue du secteur et accélérera l’appropriation des outils et process High-NA EUV.

- Engagement en capital : L’investissement de Lam Research dans ce domaine illustre clairement son engagement. Si la collaboration de cinq ans avec IBM est un mouvement stratégique, la véritable mesure restera les dépenses d’investissement de Lam ainsi que les fonds de R&D spécifiquement destinés au développement du High-NA EUV. Des hausses marquées d’investissement confirmeraient la détermination de Lam pour ce virage technologique et la confiance portée à la projection d’un marché de l’équipement de façonnage en amont à 31,16 milliards de dollars d’ici 2030.

En résumé, les progrès seront évalués sur la base de réalisations techniques incrémentielles. Le partenariat devra d’abord valider la science dans des environnements contrôlés, puis attirer des partenaires industriels pour déployer la solution à grande échelle, et enfin assurer les investissements nécessaires pour introduire de nouveaux outils sur le marché. Chacun de ces jalons représente un possible tournant sur le chemin ardu de l’innovation technologique. Suivre ces avancées offre une perspective prospective sur le moment où—et si—cet investissement fondateur commencera à porter ses fruits.

Avertissement : le contenu de cet article reflète uniquement le point de vue de l'auteur et ne représente en aucun cas la plateforme. Cet article n'est pas destiné à servir de référence pour prendre des décisions d'investissement.

Vous pourriez également aimer

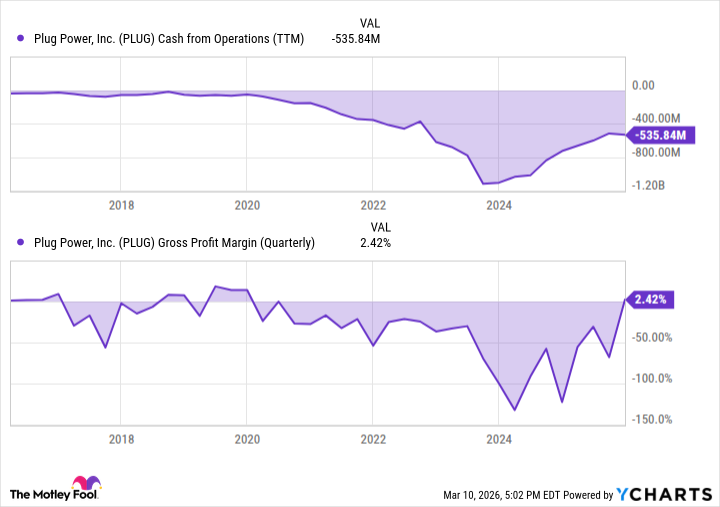

Est-ce le bon moment d’acheter des actions Plug Power alors qu’elles sont sous les 3 dollars ?

Prévision : La valeur de XRP restera en dessous de 2 $ jusqu’en 2027